半導体事業

激動するシリコンサイクルに常に最高質の人財力でお応えします

工程・装置別「業務一括請負」の流れ

- まずは数名を派遣し、貴社にて技術を修得。次いで習熟管理表を作成し、多数の当社社員に技術を伝授。必要人数の技術者が育った時点で一括請負に移行します。多工程・多機種のトラブル対応が可能。当社請求額は稼働台数に比例しますので、従来のような人員数の確保に伴う無駄な生産コストを削減できます。

- エンジニアの約9割が在籍し続ける職場。それが私たちの強みです。

半導体大手S社様のケース

生産現場のニーズに確実にお応えする当社エンジニアの高いサポート力が認められ、グループ企業数千社の中から当該企業様で初めての社長賞を受賞。

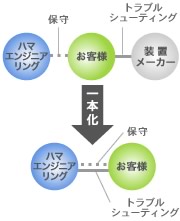

トラブルシューティングにも幅広く対応

- 装置の導入や修理は装置メーカーへ。保守・保全は製造系派遣会社へ。こうした日々の煩雑な管理運営業務が企業様の大きな負担になっているのが現状です。この事はコスト高の原因のひとつにもなっています。

- 当社がお引き受けする業務領域は保守・保全が原則ですが、メンテナンスの枠を超えて多彩なトラブルシューティングにも対応できる総合力が、他社には無い大きな強みになっています。いわば、ワンストップショッピングならぬワンストップエンジニアリング。修理対応も含めた広い対応力で、企業様のニーズを一手に担います。

半導体製造装置大手T社様のケース

装置の保守・保全はもちろん、ライン構築のお手伝いから搬入・導入の管理・立ち会い、トラブルシューティングに至るまで総合的に任されています。

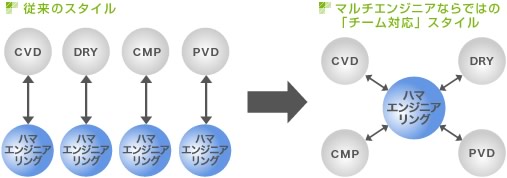

コストパフォーマンスを向上させる「マルチエンジニア」を育成

エンジニアが有する技能は現在でも「一工程」が主流ですが、当社には「多工程・多機種」に対応するマルチエンジニアが多数スタンバイ。今回はPVD、次はCMPというように、個々のエンジニアが生産計画の変化に柔軟に対応できるので、技術レベルを下げることなく、マンパワーに係るコストを節減できます。

半導体ができるまで

半導体は、電化製品・ゲーム・パソコン・携帯電話などの様々な製品に使われ、私たちの生活を豊かにしています。

半導体は、電気が流れたり、流れなかったりする性質を持つので、この性質を利用して電圧をかけたときだけ電気が流れる仕組み(トランジスタ)を作ります。

そして何千万個ものトランジスタが組み合わされて1つの集積回路(LSI)ができます。

小型化、高度化する電子機器になくてはならない半導体ができるまでの工程を、イラストでわかりやすくご紹介しています。

ICの製造工程

ICの製造工程は下記のように大きく分けて3つに分かれます。

それぞれの工程をクリックすることで詳細を確認することができます。

-

設計 / マスク作成

「設計/マスク作成工程」ではICの機能を決定した後回路の設計をおこない、その回路に基づきICを製造するためのマスクを作成します。

半導体設計用装置

マスクレチクル用製造装置

-

前工程

(ウエハー処理)ウェハーの上に多数のICチップを同時に作りこむ工程。拡散工程とも言われます。

ウェハー製造用装置

ウェハープロセス用処理装置

-

後工程

(組立・検査)前工程のウェハーを一個一個のチップに切り分けた後、ICチップをパッケージに収納する以降の工程。組立工程、仕上げ工程、選別工程、バーンイン工程、検査工程が含まれます。

半導体組立用装置設計用装置

検査用装置

設計/マスク作成

「設計/マスク作成工程」ではICの機能を決定した後回路の設計をおこない、その回路に基づきICを製造するためのマスクを作成します。

半導体設計用装置

回路設計・パターン設計

お客様の要求機能に応じたさまざまな回路を組み合わせ、パターンの設計をします。

はじめに開発計画に基づいてICの機能や性能 を決定し、その機能を実現するために論理回路設計をおこないます。論理回路を作成し、完成した論理回路図に対してシミュレーションを繰り返しおこない、動作を確認します。 動作に問題がなければ、論理回路図からCADを使用して実際の素子と配線のパターンとなるレイアウト設計を行い、マスク用図面を作成します。

マスクレチクル用製造装置

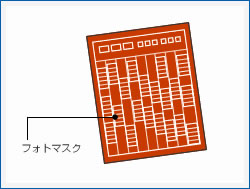

フォトマスク作成

このフォトマスクでウェハーの表面に回路のパターンを焼き付けます。

IC回路を前工程に反映させるためにはウェハー上に設計図を転写するフォトマスクが必要となります。 フォトマスクはガラス基板上に金属の薄膜で回路パターンを描画したものです。マスクはICパターンをウェハーに焼付けするための写真のネガに相当します。

前工程(ウェハー処理)

ウェハーの上に多数のICチップを同時に作りこむ工程。拡散工程とも言われます。

ウェハー製造用装置

-

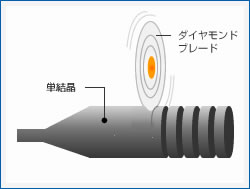

インゴットの引き上げ/切断

インゴットを切断します。インゴットはとても硬いので特殊なダイヤモンドプレートをつかって切断します。

半導体材料を薄く切り出した円盤をウェハーと呼び、ICの基板として使用されます。ウェハーの作成手順は原料となる高純度のシリコンの種から単結晶の塊(インゴット)に結晶成長させ、必要な太さの単結晶棒(インゴット)をつくります。

上下端を切り落したのち、インゴットをダイヤモンドブレードで1枚づつ円盤状に切断します。 -

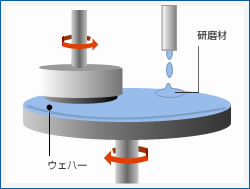

ウェハーの研磨

ウェハーが鏡状になっていないと回路パターンの品質が保てません。

仕上げとしてウェハー表面を鏡面状に研磨・洗浄してウェハーメーカから出荷されます。

ウェハープロセス用処理装置

-

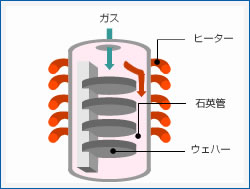

ウェハーの表面を酸化

回路パターンを焼きつけるためにウェハーに酸化膜をつけます。

ウェハーの準備が整ったら、ウェハー上に設計/マスク作成段階で設計した回路パターンを形成していきます。パターン形成手順ではまずはトランジスタのゲート絶縁膜、配線層間の絶縁膜形成に用いるため、高温の拡散炉(900°C~1,100°C)にウェハーを挿入し、酸素または水蒸気をシリコンと反応させることでウェハー表面に酸化膜を成長させます(熱酸化法)。

-

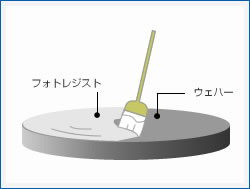

フォトレジスト塗布

フォトレジストという感光剤をウェハーの表面に塗布します。

パターン形成手順ではフォトマスクを通して光を照射する「リソグラフィー」の手法が用いられます。 この作業に備えてフォトレジストという樹脂をウェハー全体に極めて薄く均一に塗布して感光性を持たせます。

-

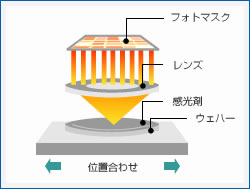

ウェハー表面にパターン形成

いよいよウェハーの表面に回路を焼き付けます。写真の原理を使い、レンズで極小に焼きつけます。

フォトレジストが塗布されたウェハーに「設計 / マスク作成」で作成したフォトマスクを重ねて光を照射し、回路図を転写します。 ウェハーとマスクの位置を合わせ、マスクの上から紫外線を照射します。フォトマスクにマスクされていない部分のみ紫外線が透過し、フォトレジストが化学的に変化します。

フォトレジストは「露光工程」の時にマスクしていない回路の部分のみ化学反応を起こして現像液に溶ける構造になっています(ポジ方式)。現像液が露光により化学変化した部分のフォトレジストを溶かします。 現像ののち、ウェハー表面にマスクパターン通りにフォトレジストが残ります。 これをレジストパターンと呼びます。 -

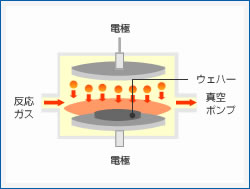

エッチング

エッチングでいらない酸化膜をとります。

エッチングで部分的に酸化膜を除去します。その後、不要なレジストも取り除きます。

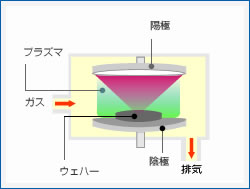

エッチングとはレジストパターンをマスクにして酸化膜や金属膜などを物理的または化学的に食刻加工することです。エッチングに薬液を用いるものをウェットエッチング、ガスによるものをドライエッチングと呼びます。 酸化膜は薬品中で、また、金属膜はプラズマ状態の中に置くことでエッチングされます。 -

酸化・拡散・CVD・イオン注入

ウェハーに素子をつくり込みます。必要なイオンを打ち込んで素子をつくります。

まず素子間を電気的に分離するために素子が形成される活性領域の周囲に素子間分離層(フィールド酸化膜)を形成します。 シリコン基板上に酸化膜および窒化膜を成長させた後、素子間分離層となる領域にレジストパターンを形成し、それをマスクにしてイオン注入を行い、P型の拡散層を形成します。(素子がN型トランジスタの場合)。次にその拡散層上の酸化膜および窒化膜をエッチングし、窒化膜のパターンをマスクにして素子間分離層となる酸化膜を成長させます。素子が形成される活性領域上に残った窒化膜と酸化膜はエッチングします。このように、ウェハーにイオンを注入(ボロン、リン)や高温拡散を行うとシリコンが出ている部分だけが半導体になります。

-

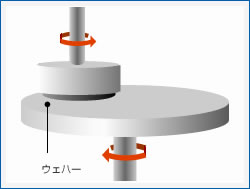

平坦化(CMP)

ウェハーの表面をきれいにします。

ウェハー表面を研磨し、パターンの凹凸を平坦化します。

-

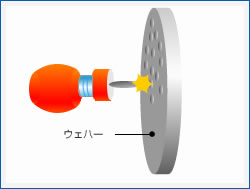

電極形成

ウェハーの表面に電極配線用のアルミ金属膜をつくります。

不活性ガスプラズマによりアルミターゲットをスパッタリングし、 ウェハー表面に電極配線用のアルミ金属膜を形成します。

-

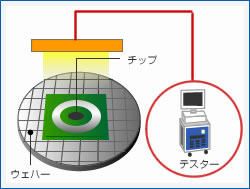

ウェハー検査

1枚のウェハーにたくさんの回路パターンができました。これを検査してからダイヤモンドプレートで切り分けます。

完成したウェハー上の各ICをテスターで電気的に検査します。 検査を終えて前工程が終了します。 ICチップのボンディングパッド(電極)にテスターからプローバーと呼ばれる探針を用いて電気信号を送り、ICチップの動作の良否を判定します。

良品・不良品の確定をし、不良品にはマークをつけます。

後工程(組立・検査)

前工程のウェハーを一個一個のチップに切り分けた後、ICチップをパッケージに収納する以降の工程。組立工程、仕上げ工程、選別工程、バーンイン工程、検査工程が含まれます。

-

組立用装置

-

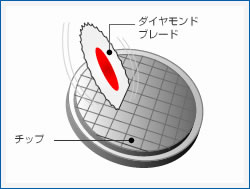

ウェハーのダイシング

ウェハーを切断し仕上がりをチェックして、良品だけが、チップとして使われます。

ウェハーを、後工程では1つ1つのICチップに切り離し、パッケージに封入していきます。 このチップの切り離し作業を「ダイシング」と呼びます。

-

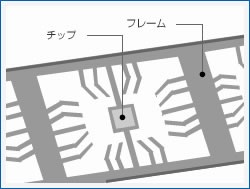

チップのマウンティング

チップが所定の位置からズレないようにしっかりと固定します。

一つ一つに切り離されたICチップをパッケージに封入します。 はじめにICチップをリードフレームと呼ばれる台と接続します。そのために固定する作業をマウンティングと呼びます。 リードフレームはICチップを載せる場所(アイランド)と、チップの電極と繋がる場所(リード)から成っています。 アイランドの上に銀ペースト樹脂をのせてからICチップを軽く押しつけて接着します。

-

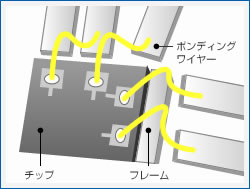

ワイヤーボンディング

チップとリードフレームをボンディングワイヤーで結びます。とても精度の高い技術が要求されます。

マウントされたICチップとリードフレームを接続します。この工程をボンディングと呼びます。 接続にはあらかじめ電極の相対位置関係をプログラム入力したボンディング装置を用います。金細線を用いてICチップ周辺部の電極とリードフレーム上のリードを接続します。

-

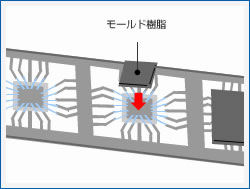

モールド

チップにキズや衝撃を抑えるためにセラミックやモールド樹脂でパッケージしてガードします。

ICチップとリードフレームのアイランドをセラミック、モールド樹脂などで封入して保護します。これによりゴミや水分などからICチップを守ることができます。 ICチップの載ったリードフレームを金型にセットし、高温で液状化した樹脂を封入します。 そののちリードフレームを切断して1個1個のパッケージに分離します。

-

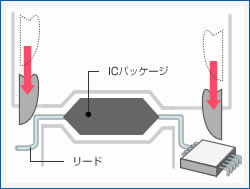

トリム&フォーム

半導体が完成するまで重要なテストをうけます。

金型にて、リードフレームから個々の半導体製品を切断・分離し、 外部リードを所定の形状に成型します。

-

-

検査用装置

-

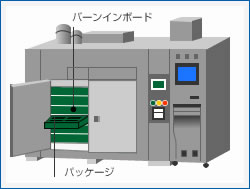

バーンイン(温度電圧試験)/製品検査・信頼性試験

バーインボードにパッケージをセットして湿度と温度のテストをします。

パッケージ化されたICをテストを通じて選別します。初期不良を除くため、ファンクションテストを行いながら温度電圧ストレスの加速試験を行います。 試験される特性には、直流特性と機能特性があります。 テストにあたって分離されたパッケージをテスターにセットし、予め準備されたプログラムに従って直流特性と機能特性が測定されます。

-

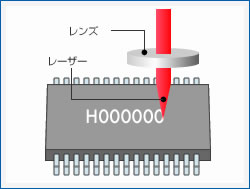

マーキング

半導体への印字はレーザーでします。

IC製造の最後の段階として、パッケージ表面への印字とリード形状の加工がおこなわれます。この工程でICが完成します。 印字にはレーザー光線を用いて樹脂の表面数ミクロンを彫り込みます。印字されるのは製品名・メーカー名などの情報です。 続いてパッケージの周囲から出ているリードを最終的な製品の形に加工します。

-

半導体完成

-

これで完成! みんなが使っているパソコンや電化製品の半導体はこうして作られています。